Eleganter Adreßdecoder für GENIE 1

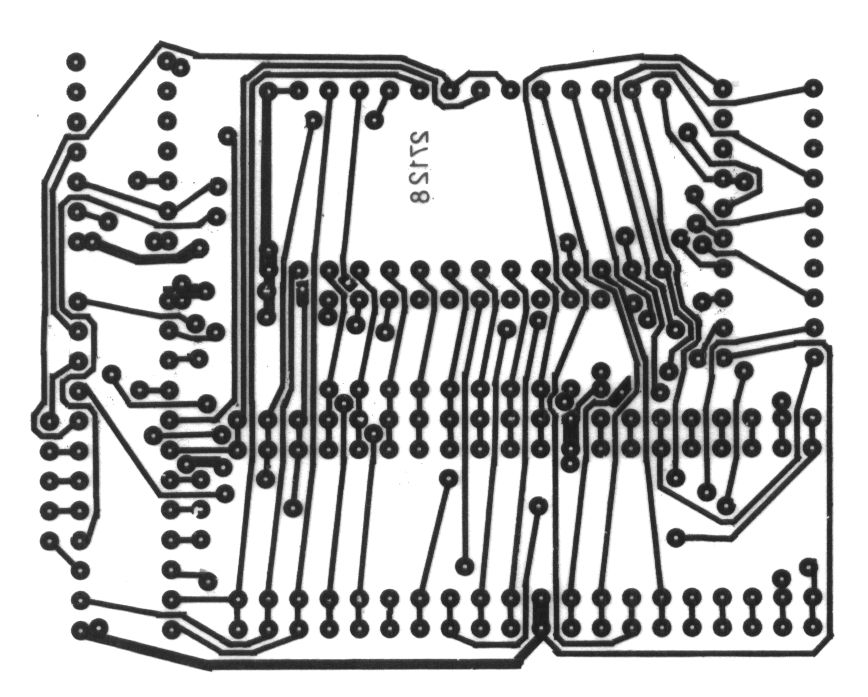

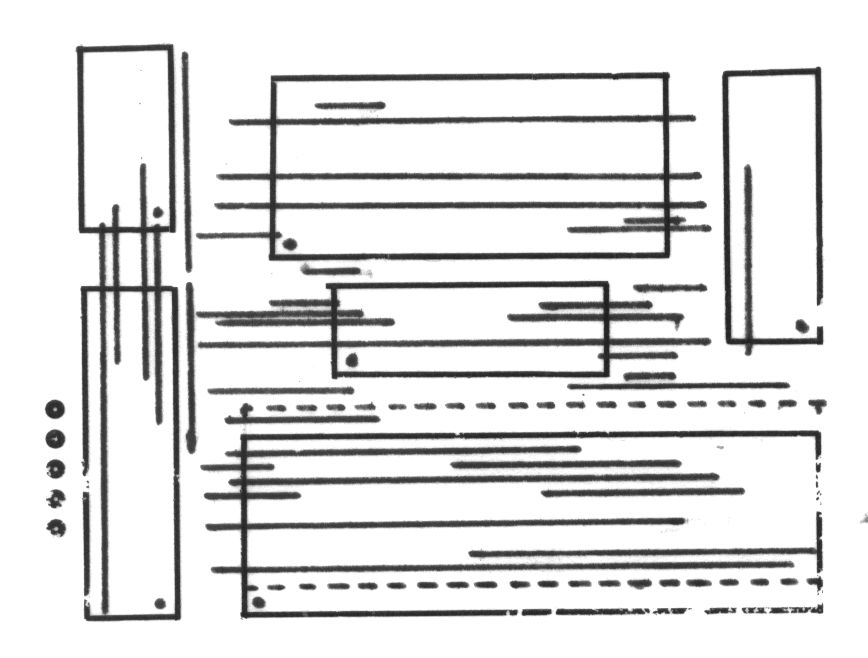

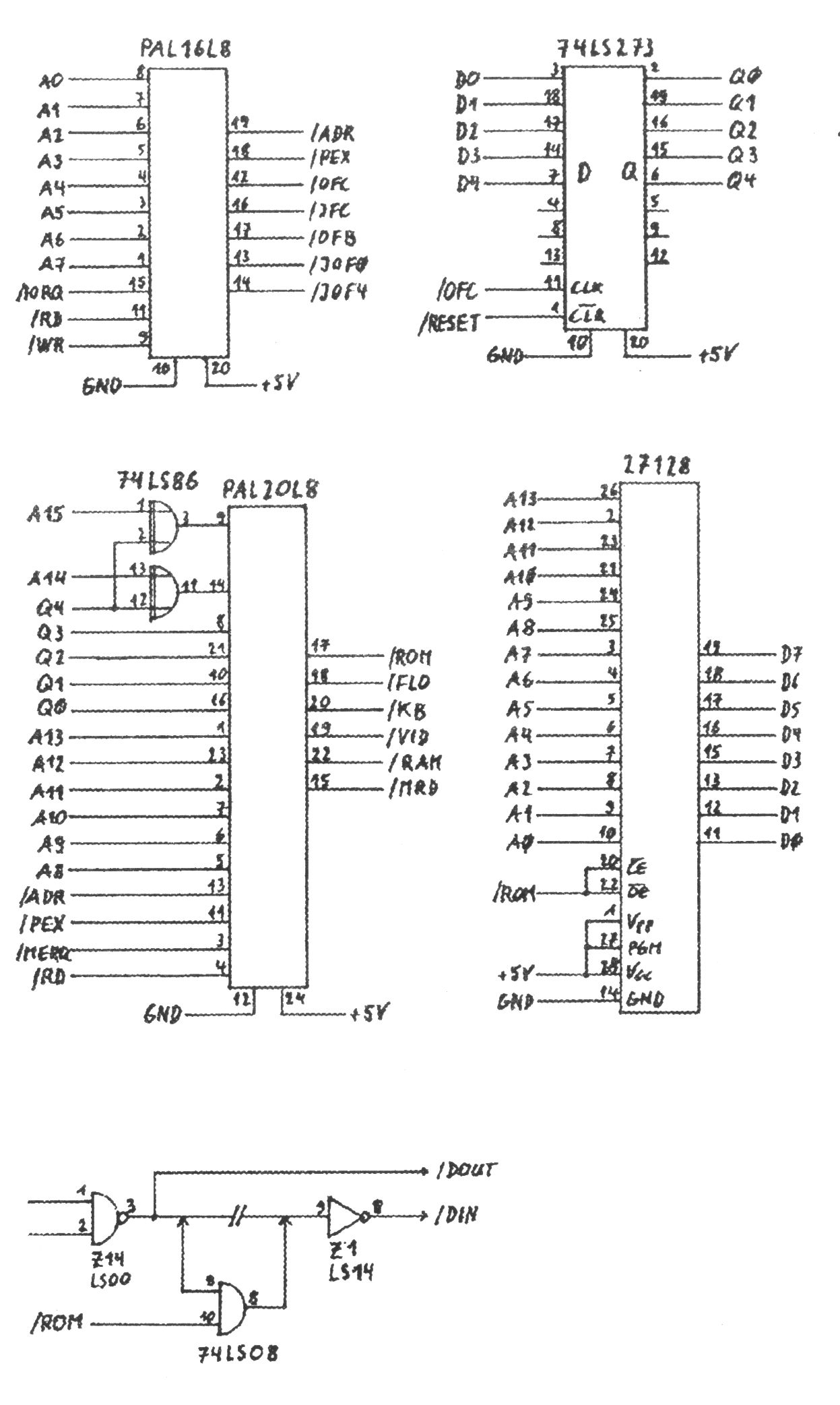

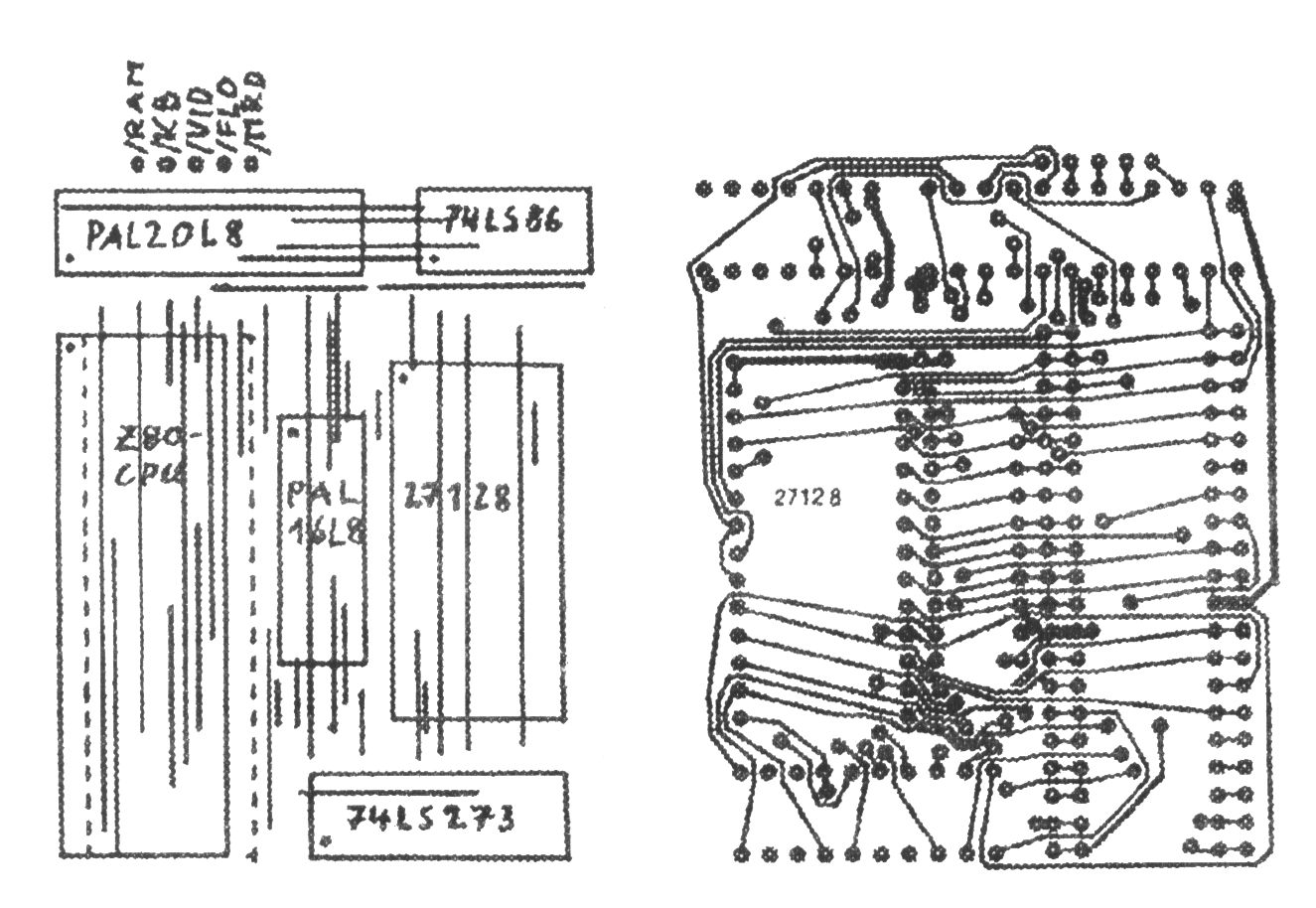

Helmut BernhardtAls ich bei der Fehlersuche in meinem GENIE 1 durch die zahlreichen selbstgeschnitzten Erweiterungen und das damit verbundene Strippengewirr selbst nicht mehr durchblickte, keimte der Gedanke, das alles sehr viel übersichtlicher und völlig neu zu gestalten. Als Ergebnis kam ein kleines Board heraus, das in den Sockel des Z80 zu stecken ist und den Z80 selbst mit aufnimmt. Zusätzlich wird auf dem Board ein 27128-EPROM (das anstelle der dann überflüssigen Original-ROMs das Level-II-Basic enthält), ein 74LS273-Latch, ein PAL16L8 (das ein Freigabesignal für das 74LS273 und einige zusätzliche Freigabesignale erzeugt) und ein Adreßdecoder-PAL20L8 (das die Freigabesignale für alle memory mapped Systemkomponenten erzeugt) untergebracht.

Die Ausgänge des Latch 74LS273 haben folgende System-Steuerfunktionen:Q0 = 0 : 0000H-2FFFH ist beim Lesen ROM und beim Schreiben RAM

= 1 : 0000H-2FFFH ist beim Lesen und Schreiben RAM

Q1 = 0 : 37E0H-37EFH ist Floppy, Drucker, INT-Status, Drive-Select

= 1 : 37E0H-37EFH ist RAM; Floppy u.s.w. sind über die Ports E0H- EFH erreichbar

Q2 = 0 : 3800H-38FFH ist beim Lesen die Tastatur und beim Schreiben RAM

= 1 : 3800H-38FFH ist beim Lesen und Schreiben RAM

Q3 = 0 : 3C00H-3FFFH ist Video-RAM

= 1 : 3C00H-3FFFH ist RAM

Q4 = 0 : die memory mapped Systemkomponenten liegen im Bereich 0000H-3FFFH

= 1 : die memory mapped Systemkomponenten liegen im Bereich C000H-FFFFH

|

Unabhängig vom Zustand von Q0-Q4 ist dauerhaft bei 3000H-37DFH, 37F0H- 37FFH und 3900H-3BFFH RAM eingeblendet. Anstelle eines Sonder-ROM war mir RAM bei 3000H wichtiger. Das Board erzeugt die Freigabe-Signale /ROM, /RAM, /FLO, /KB und /VID und das Steuersignal /MRD für die Lesetreiber des RAMs. Diese Signale sind an die entsprechenden Punkte auf dem CPU-Board zu führen; die ursprünglichen Signale sind zu durchtrennen. Layout Drahtbrücken

|

Schaltplan

|

Frei zum CPU-Board und zum RB-EXP1 zu verdrahtende Signale

| Signal | Pin des 20L8 | zu verbinden mit | zu durchtrennende Leitung | |

| /RAM | 22 | Z37,74LS367,Pin15 | von Z36,74LS04,Pin2 | #1 |

| /MRD | 17 | Z9,74LS367,Pin1 | von Z21,74LS20,Pin8 | #2 |

| /KB | 20 | Z7,74LS368,Pin1 | von Z35,74LS32,Pin3 | |

| /VID | 19 | Interboard-Conn. Pin10 | von Z37,74LS32,Pin11 | |

| /FLO | 18 | RB-EXP1, Z18, 74LS15,Pins2,14 | RB-EXP1, Z14, 74LS32,Pin11 | #3 |

| #1 | bei Aufrüstung auf 64K (256K) RAM besteht diese Verbindung als freie Verdrahtung; dieser Draht wird entfernt |

| #2 | bei Entfernen von Z21,74LS20 entfällt das Durchtrennen |

| #3 | Z13,74LS30 auf dem EXP1 kann entfernt werden anstelle von /MWR von Z15,74LS32,Pin3 auf dem CPU-Board muß /BWR von Z16,74LS367,Pin11 an das EXP1 geführt werden, damit der Betrieb über die Ports E0H-EFH möglich ist |

Das Freigabesignal /ROM ist auf dem Huckepack-Board direkt an die Pins 20 und 22 des EPROMs geführt.

Die Erzeugung dieser Freigabesignale ist aus dem Assembler-Listing für das PAL20L8 zu ersehen. Die Adreßeingänge A14 und A15 dieses PALs sind nicht die Adressen A14 und A15 der CPU. Diese Signale werden aus 2 XOR-Gattern (74LS86) aus den Adressen A14 und A15 der CPU erzeugt. Mit Q4 des Latch läßt sich damit steuern, ob A14 und A15 invertiert oder direkt an das PAL gelangen.

PAL-Assembler-Listing für das Adreßdecoder PAL20L8PAL20L8 GENIE 1 Adreßdecoder mit mm-I/O-Switching

04.09.88 H. Bernhardt

A13 A11 MERQ RD A8 A9 A10 Q3 A15 Q1 PEX GND

ADR A14 MRD Q0 ROM FLO VID KB Q2 RAM A12 VCC

/ROM = /Q0 */MERQ */RD */A15 */A14 */A13

+ /Q0 */MERQ */RD */A15 */A14 * A13 */A12

/FLO = /Q1 */MERQ */A15 */A14 *A13 *A12 */A11 *A10 *A9 *A8 */ADR + Q1 */PEX

/KB = /Q2 */MERQ */RD */A15 */A14 *A13 *A12 *A11 */A10 */A9 */A8

/VID = /Q3 */MERQ */A15 */A14 *A13 *A12 *A11 *A10

/RAM = /MERQ *ROM *FLO *KB *VID

/MRD = /MERQ */RD *ROM *FLO *KB *VID

Um bei den zur Verfügung stehenden Pins des PAL20L8 auch das Signal /FLO voll ausdecodieren zu können (A4-A15), mußte eine Gruppe von Adressen (A4-A7) schon zusammengefaßt (/ADR) und an einen Pin des PALs geführt werden. Auch für das alternativ von einer Portadresse herzuleitende /FLO war ein vorheriges Ausdecodieren von /IORQ, A4-A7 nötig (/PEX). Diese Signale werden vom PAL16L8 erzeugt, an das für das Erzeugen von /OUTFC (Freigabe des Steuer-Latch) ohnehin schon die Adressen A0-A7 und /IORQ gelangen.

PAL-Assembler-Listing für das I/O-Decoder-PAL16L8PAL16L8

GENIE 1 Portdecoder

04.09.88 H.Bernhardt

A7 A6 A5 A4 A3 A2 A1 A0 WR GND

RD OFC IOF0 IOF4 IORQ IFC OFB PEX ADR VCC

| /OFC | = /IORQ */WR *A7 *A6 *A5 *A4 *A3 *A2 */A1 */A0 | ;Pin12 |

| /IFC | = /IORQ */RD *A7 *A6 *A5 *A4 *A3 *A2 */A1 */A0 | ;Pin16 |

| /OFB | = /IORQ */WR *A7 *A6 *A5 *A4 *A3 */A2 *A1 *A0 | ;Pin17 |

| /IOF0 | = /IORQ *A7 *A6 *A5 *A4 */A3 */A2 | ;Pin13 |

| /IOF4 | = /IORQ *A7 *A6 *A5 *A4 */A3 *A2 | ;Pin14 |

| /PEX | = /IORQ *A7 *A6 *A5 */A4 | ;Pin18 |

| /ADR | = A7 *A6 *A5 */A4 | ;Pin19 |

Da das PAL16L8 noch einige freie Ausgangs-Pins hatte, wurden noch einige weitere Port-Freigabe-Signale decodiert.

Funktion der Port-Freigabesignale des PAL16L8| /OFC (/OUT FCH) | wird intern zur Freigabe des Sytem-Steuerlatch benutzt |

| /IFC (/IN FCH) | steht für die Freigabe eines über Port FCH zu lesenden Treibers zur Verfügung |

| /OFB (/OUT FBH) | Freigabe-Signal, um über Port FBH ein Latch zu be schreiben; kann für die Freigabe des 74LS273 (Pin11) auf dem 256K-Banker benutzt werden (A0-A5 brauchen dann nicht mehr zum Banker geführt zu werden, A6 und A7 sind für das Erzeugen einer 8Bit-Refreshadresse dort aber weiterhin nötig; das 74LS30 auf dem Banker kann entfallen) |

| /IOF0 und /IOF4; (/In/OUT F0H-F3H; /IN/OUT F4H-F7H) | Freigabe-Signale für z.B. Z80-Peripherie-Bausteine mit 4-Portadressen (PIO, SIO, CTC, DMAC, PPI8255...) |

Die Verwendung eines 27128-EPROMs (wovon es auch 150ns-Versionen gibt) erlaubt bedeutend höhere Taktraten als die ursprünglichen ROMs. Wenn dann auch noch das Timing der Signale /RAS, /MUX und /CAS anders gelöst wird, spielen auch die RAMs mit. 5,3MHz sind auch ohne große Eingriffe möglich.

Da das ROM nun innerhalb der Treiber der CPU-Signale liegt, muß zur Steuerung der Daten-Lesetreiber auch das Signal /ROM herangezogen werden. Diese Treiber dürfen nicht freigegeben werden, wenn das ROM gelesen wird.

Um dies zu erreichen, wird Pin9 von IC1,74LS14 durchgekniffen und hochgebogen. Auf IC1 wird ein 74LS08 mit den Pins 7 und 14 huckepack aufgelötet. Alle anderen Pins des 74LS08 werden hochgebogen. Der abgekniffenen und hochgebogene Pin9 des IC1 wird mit dem seitlich gebogenen Pin8 des 74LS08 verlötet. Pin10 des 74LS08 wird mit Pin22 des 27128-EPROMs und Pin9 des 74LS08 mit Pin3 von IC14,74LS00 verbunden (Abbildung).

Zur Freigabe der Speicherlese-Treiber erzeugt das PAL20L8 das Signal /MRD, das an Pin15 von IC9,74LS367 zu legen ist. Durch Entfernen von IC21,74LS20 wird das bisherige Signal entfernt.

Außer IC21 sind auch IC22,74LS156 und IC25,74LS139 überflüssig geworden. Diese ICs können ebenfalls entfernt werden. Und natürlich können auch die alten ROMs rausgeschmissen werden.

Beim Aufbau des Huckepack-Boards sind folgende Punkte zu beachten:Vor dem Einlöten irgendwelcher Bauteile sind zunächst sämtliche Drahtbrücken zu legen. Als erstes sind dann der Sockel für den Z80 und der Stecker für das Anflanschen des Boards in den Z80-Sockel auf dem CPU-Board in geeigneter Reihenfolge einzulöten. Der Stecker wird auf der Lötseite und der Sockel auf der Bestückungsseite eingebaut. Dabei erschwert das zuerst eingebaute Teil den Einbau des anderen. Was zuerst angelötet wird, sollte eine gründliche Besichtigung der Teile ergeben.

Es sollten alle ICs gesockelt werden. Sowohl beim EPROM als auch bei den PALs kann irgendwann der Wunsch nach geändertem Inhalt aufkommen. Und für Testzwecke bei der Fehlersuche ist es auch bei Standard-ICs zweckmäßig, wenn man diese auswechseln kann oder einfach nur einzelne Pins aus der Fassung biegen kann.

Ungebohrte Boards, mit Level-II befüllte 27128-EPROMs und gebrannte PALs kann ich zum Selbstkostenpreis zur Verfügung stellen.